Clamping Circuit Lab Manual

Diode Clamping Circuit In this article, the working of a clamping circuit is explained. The working of different clamping circuits like positive and negative clamper, with circuit diagrams and waveforms, are given below. Related Articles A clamping circuit is used to place either the positive or negative peak of a signal at a desired level. The dc component is simply added or subtracted to/from the input signal. The clamper is also referred to as an IC restorer and ac signal level shifter. In some cases, like a TV receiver, when the signal passes through the capacitive coupling network, it loses its dc component. This is when the clamper circuit is used so as to re-establish the dc component into the signal input.

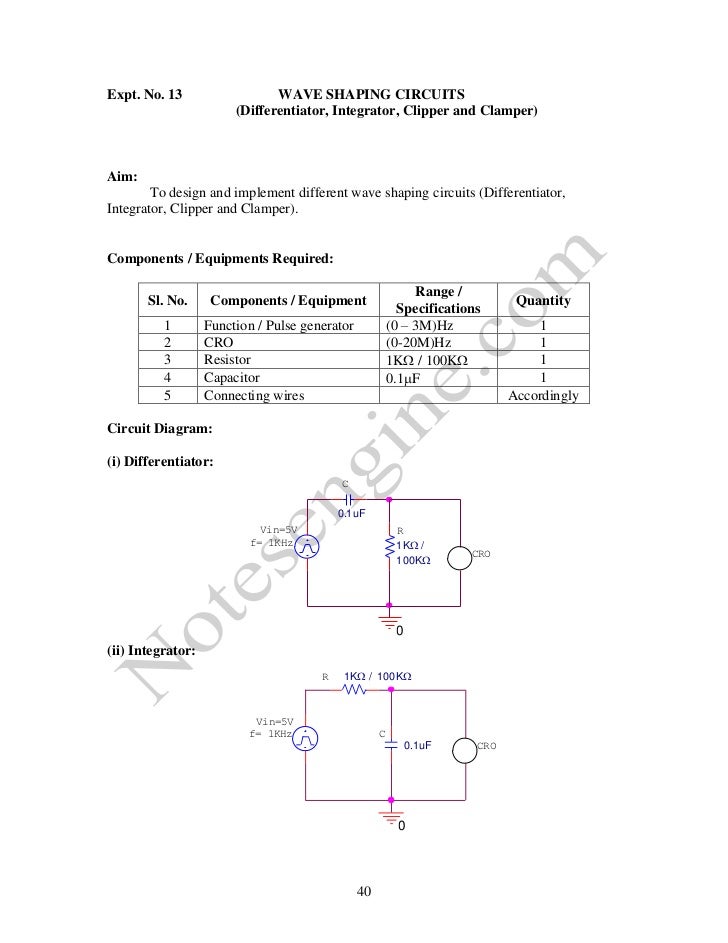

Though the dc component that is lost in transmission is not the same as that introduced through a clamping circuit, the necessity to establish the extremity of the positive or negative signal excursion at some reference level is important. Types of clamping circuits A clamp circuit adds the positive or negative dc component to the input signal so as to push it either on the positive side, as illustrated in figure (a) or on the negative side, as illustrated in figure (b).

Positive clamper The circuit will be called a positive clamper, when the signal is pushed upward by the circuit. When the signal moves upward, as shown in figure (a), the negative peak of the signal coincides with the zero level. Negative Clamper The circuit will be called a negative clamper, when the signal is pushed downward by the circuit. When the signal is pushed on the negative side, as shown in figure (b), the positive peak of the input signal coincides with the zero level. Working of a diode clamping circuit For a clamping circuit at least three components — a diode, a capacitor and a resistor are required. Sometimes an independent dc supply is also required to cause an additional shift. The important points regarding clamping circuits are: (i) The shape of the waveform will be the same, but its level is shifted either upward or downward, (ii) There will be no change in the peak-to-peak or rms value of the waveform due to the clamping circuit.

Thus, the input waveform and output waveform will have the same peak-to-peak value that is, 2V max. This is shown in the figure above. It must also be noted that same reading will be obtained in the ac voltmeter for the input voltage and the clamped output voltage. (iii) There will be a change in the peak and average values of the waveform. In the figure shown above, the input waveform has a peak value of V max and average value over a complete cycle is zero. The clamped output varies from 2 V max and 0 (or 0 and -2V max).

Thus ths peak value of the clamped output is 2V max and average value is V max. (iv) The values of the resistor R and capacitor C affect the waveform. (v) The values for the resistor R and capacitor C should be determined from the time constant equation of the circuit, t = RC. The values must be large enough to make sure that the voltage across the capacitor C does not change significantly during the time interval the diode is non-conducting.

In a good clamper circuit, the circuit time constant t = RC should be at least ten times the time period of the input signal voltage. It is advantageous to first consider the condition under which the diode becomes forward biased. Clamping circuits are often used in television receivers as dc restorers. The signal that is sent to the TV receiver may lose the dc components after being passed through capacitively coupled amplifiers.

Thus the signal loses its black and white reference levels and the blanking level. Before passing these signals to the picture tube, these reference levels have to be restored. This is done by using clamper circuits. They also find applications in storage counters, analog frequency meter, capacitance meter, divider and stair-case waveform generator. Consider a negative clamping circuit, a circuit that shifts the original signal in a vertically downward direction, as shown in the figure below.

The diode D will be forward biased and the capacitor C is charged with the polarity shown, when an input signal is applied. During the positive half cycle of input, the output voltage will be equal to the barrier potential of the diode, V 0 and the capacitor is charged to (V – V Q). During the negative half cycle, the diode becomes reverse-biased and acts as an open-circuit. Thus, there will be no effect on the capacitor voltage. The resistance R, being of very high value, cannot discharge C a lot during the negative portion of the input waveform. Thus during negative input, the output voltage will be the sum of the input voltage and the capacitor voltage and is equal to – V – (V — V 0) or – (2 V – V 0). The value of the peak-to-peak output will be the difference of the negative and positive peak voltage levels is equal to V 0-(2V-V 0) or 2 V.

The figure shown below can be modified into a positive clamping circuit by reconnecting the diode with reversed polarity. The positive clamping circuit moves the original signal in a vertically upward direction. A positive clamping circuit is shown in the figure below.

It contains a diode D and a capacitor C as are contained in a negative clamper. The only difference in the circuit is that the polarity of the diode is reversed. The remaining explanation regarding the working of the circuit is the same as it is explained for the negative clamper. To remember which way the dc level of a signal moves, look at the figure shown below. Notice that the diode arrows point downward, the same direction as the dc shift. Positive Clamping Circuit A number of clamping circuits with their effect on the input signal are shown in the figure given below. All the figures shown below have the input and output signals in square waves, the same procedure can be used for sinusoidal inputs.

Sharepoint foundation 2013 setup guide. In fact, one approach to the analysis of clamping networks with sinusoidal inputs is to replace the sinusoidal wave signal by a square wave of the same peak values. The resulting output will then form an envelope for the sinusoidal response, as illustrated in figure (g) for a network appearing in figure (f). The diodes have been assumed to be ideal and 5 RC » T/2 in drawing the output waveforms. Applications of clamping circuits. They find some applications in sonar and radar testing.

Used as voltage doublers. They are used to remove distortions in a circuit. Used in video processing equipment like TV. Wrong site for my comment, sorry🙊 Now I am obliged to give credit where due to AllAboutCircuits. I came here after going there, wanting something simple without the SPICE convention that conglomerates so many results together. I could not delete my comment discreetly, so I will scatter a bigger paper trail 👌 But I do have nice things to say about the article above — the five points and the many examples plus the arrow advice.

I saw all the diligent work on using mathematic descriptors and took note for pursuing my course. And the individual examples helped me check my knowledge. Equating signal with the ground, or common, was notable a way to show where DC level comes from that superimposure AC become commuted to. I got what I needed here 📍. Could some one enlighten me on the following?

Tank you very much! 1) from the very beginning, D is on, signal goes positive, then the other side of C should go negative, and turns D off. Why will D be on for the whole positive cycle of the signal and hold the output at the turn on voltage of D? 2) “During the negative half cycle, the diode becomes reverse-biased and acts as an open-circuit. Thus, there will be no effect on the capacitor voltage.” then why do we still count the signal as part of the output, by taking it as “the sum of the.input voltage. and the capacitor voltage”?

3) also, once D “becomes reverse-biased and acts as an open-circuit, thus, there will be no effect on the capacitor voltage”, then D will never be on again, because the signal will never has any effect on D again. Is that correct? I really need to understand how a clampinng circuit like this works, please help every one! Thank you for your presentation which is very nice. I have one thing that I need to confirm.

The polarity on the capacitor is built very quickly on the direction that the diode conduct. And because the time constant is so large, then when the input voltage change polarity this will not affect the polarity of the capacitor much. Then I should expect that this clamping is up and running after some time from firing it. I mean that the first few cycles will not be taking this shape, till the cap is fully charged.

##AIM Design and construct a suitable circuit and demonstrate the working of positive clipper, double ended clipper and positive clamper using diodes. ##COMPONENTS REQUIRED Diode (BY-127 / IN4007), Resistors- 10Kohm & 3.3kohm, DC regulated power supply (for Vref), Signal generator (for Vi) and CRO. ##CIRCUIT DIAGRAM OF POSITIVE CLIPPER ###Fig.1 a Positive clipper Circuit b. Transfer Characteristics Clippers clip off a portion of the input signal without distorting the remaining part of the waveform. In the positive clipper shown above the input waveform above Vref is clipped off. If Vref = 0V, the entire positive half of the input waveform is clipped off.

Plot of input Vi (along X-axis) versus output Vo (along Y-axis) called transfer characteristics of the circuit can also be used to study the working of the clippers. Choose R value such that where Rf = 100? And Rr = 100k? Are the resistances of the forward and reverse diode respectively. Hence R = 3.3k? Let the output resistance RL = 10k? The simulations can be done even without RL.

##PROCEDURE:. Before making the connections check all components using multimeter.

Make the connections as shown in circuit diagram. Using a signal generator (Vi) apply a sine wave of 1KHz frequency and a peak-to-peak amplitude of 10V to the circuit. (Square wave can also be applied.). Keep the CRO in dual mode, connect the input (Vi) signal to channel 1 and output waveform (Vo) to channel 2. Observe the clipped output waveform which is as shown in fig.

Glamping Circuit Lab Manual

Also record the amplitude and time data from the waveforms. Now keep the CRO in X-Y mode and observe the transfer characteristic waveform. ##Note:.

Vary Vref and observe the variation in clipping level. For this use variable DC power supply for Vref. Change the direction of diode and Vref to realize a negative clipper. For double-ended clipping circuit, make the circuit connections as shown in fig.3 and the output waveform observed is as shown in figure 5. Adjust the ground level of the CRO on both channels properly and view the ouput in DC mode (not in AC mode) for both clippers and clampers. ##WAVEFORMS Fig.

Input and output waveform for positive Clipper ##DOUBLE ENDED CLIPPER ###Fig.3 Double ended clipper Circuit b. Transfer Characteristics ###Fig. Input and output waveform for double-ended clipping circuit ##Note: ###The above clipper circuits are realized using the diodes in parallel with the load (at the output), hence they are called shunt clippers. The positive (and negative) clippers can also be realized in the series configuration wherein the diode is in series with the load. These circuits are called series clippers.

##POSITIVE CLAMPER ##COMPONENTS REQUIRED: Diode (BY-127), Resistor of 200 K?, Capacitor - 0.1?F, DC regulated power supply, Signal generator, CRO ###Fig. 5 Positive Clamper The clamping network is one that will 'clamp' a signal to a different DC level. The network must have a capacitor, a diode and a resistive element, but it can also employ an independent DC supply (Vref) to introduce an additional shift. The magnitude of R and C must be chosen such that time constant?=RC is large enough to ensure the voltage across capacitor does not discharge significantly during the interval of the diode is non-conducting. ##DESIGN: Say for t = 20msec (corresponding to a frequency of 50 Hz), then for RC t, let C=0.1µF, then R = 200K? ##PROCEDURE:. Before making the connections check all components using multimeter.

Clamping Circuit Lab Manual

Make the connections as shown in circuit diagram (fig. Using a signal generator apply a square wave input (Vi) of peak-to-peak amplitude of 10V (and frequency greater than 50Hz) to the circuit. (Sine wave can also be applied). Observe the clamped output waveform on CRO which is as shown in Fig. ##Note:.

For clamping circuit with reference voltage Vref, the output waveform is observed as shown in Fig. For without reference voltage, Keep Vref = 0V. CRO in DUAL mode and DC mode. Also the grounds of both the channels can be made to have the same level so that the shift in DC level of the output can be observed.

For negative clampers reverse the directions of both diode and reference voltage. 6 Input and output waveform for positive clamper without reference voltage. 7 Input and output waveform for positive clamper circuit with reference voltage = 2V Go.

Latest Posts

- ✔ Belarus Tractor Operators Manual

- ✔ Grasso Refrigeration Screw Compressor Manual

- ✔ 1993 Yamaha 115 Hp Outboard Owners Manual

- ✔ Mbe4000 Service Manual

- ✔ Mercedes Benz E350 Owners Manual

- ✔ Bombardier Quest 650 Xt 2015 Manual

- ✔ Motor Grader Operator Manual

- ✔ Singer Sewing Machine Repair Manuals Model 14sh654

- ✔ Ib Grade 8 Study Guide

- ✔ Eei Study Guide

- ✔ Chevy Aveo 2016 Service Manual

- ✔ 207 Mercedes Benz Repair Manual

- ✔ Manual For Serger

- ✔ Yamaha Yfm 600 Grizzly Service Manual

- ✔ 2016 Toyota Corolla Ascent Workshop Manual

- ✔ Digital Signal Processing Solution Manual Proakis Manolakis

- ✔ Kymco Sento Manual

- ✔ M109r Suzuki Parts Manual

- ✔ 06 Xl1200r Service Manual

- ✔ Pearson Social Studies Grade 4 Pacing Guide

- ✔ 2015 Toyota Camry Owner Manual

- ✔ Mercruiser 135 Hp Manual

- ✔ 2018 Big Red Owners Manual